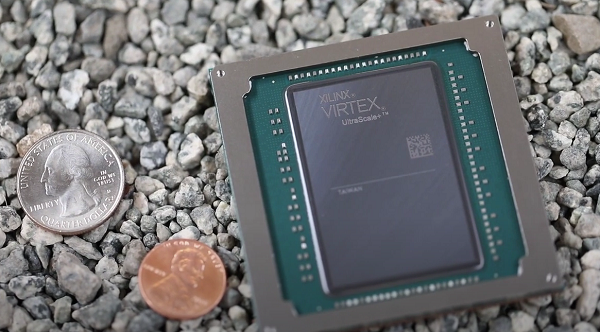

Cursul prezinta circuitele cunoscute sub numele de FPGA (Field-Programmable Gate Array) si respectiv CPLD (Complex Programmable Logic Device), cu accentul pus pe circuitele unuia din producatorii reprezentativi de astfel de circuite, firma Xilinx.

Se presupune ca cititorul este familiarizat cu circuitele programabile clasice de tip PLD (cum ar fi PAL sau GAL) cunoscute si sub denumirea de SPLD (Simple Programmable Logic Device).

Ce sunt circuitele FPGA si CPLD?

Pastrand proportiile am putea spune ca circuitele FPGA si CPLD sunt echivalentul modern al placilor universale de testare (breadboard) pe care erau montate circuite numerice simple (porti, bistabile, etc.) care puteau fi apoi interconectate prin intermediul unor fire de catre utilizator pentru a testa o anumita aplicatie.

Afirmatia va fi, evident, justificata in cele ce urmeaza. Inainte de a aborda problematica specifica trebuie mentionate si circuitele cunoscute sub denumire de ASIC (Application-Specific Integrated Circuit).

Ce sunt circuitele ASIC?

ASIC este un circuit integrat complex dedicat implementarii unei aplicatii particulare, mai degraba decat unei utilizari generale. Un circuit ASIC este proiectat de o anumita companie si este realizat pentru un singur beneficiar (client).

Cresterea exponentiala a densitatii de integrare a circuitelor VLSI face posibila integrarea aproape a tuturor sub sistemelor numerice imaginabile.

Ce include un circuit ASIC?

Un circuit ASIC poate include un microprocesor de 32 de biti impreuna cu memorie si periferice complexe, caz in care mai poate fi referit si ca un SoC (System on Chip) prin care se intelege un sistem de calcul realizat pe un singur microcircuit.

SoC este in realitate o notiune foarte larga tinand cont ca printre periferice se pot numara sisteme analogice complexe, senzori de tip MEMS (bazati pe micro sau nano tehnologii mecanice) si chiar sisteme de radiofrecventa performante.

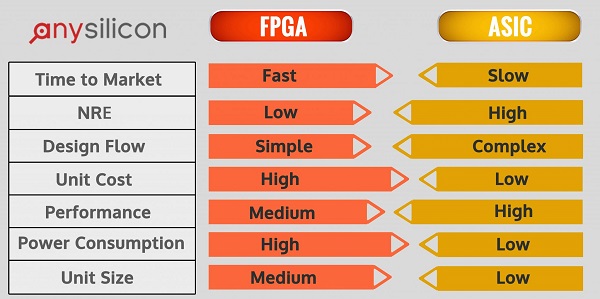

Care sunt diferentele dintre FPGA si ASIC?

Un exemplu tipic de ASIC si SoC in acelasi timp este un circuit cu ajutorul carora se realizeaza cea mai mare parte a unui telefon mobil.

Argumentele in favoarea conceptului SoC seamana acum cu cele care, cu mult timp in urma, justificau dezvoltarea circuitelor integrate numerice: scaderea dimensiunilor, reducerea consumului energetic si cresterea fiabilitatii comparativ cu sistemele care utilizau mai multe componente, reducerea costurilor legate de montare, totul la o alta scara de complexitate.

Ce sunt circuitele ASSP?

ASSP (Application Specific Standard Product) este tot un circuit integrat similar ASIC dedicat unei anume piete de aplicatii, dar destinat mai multor utilizatori (de aici si „standard”).

Circuitele de tip ASSP sunt destinate mai multor clienti pentru ca sunt de uz general, dar numarul acestora este mic pentru ca aplicatia este una specifica.

Un aspect important legat de circuitele ASIC sunt costurile legate de pregatirea fabricatiei si partial de proiectarea lui. Costurile respective referite drept costuri NRE (Non Recurring Engineering) sunt uzual foarte mari (x 100000 USD) chiar si pentru un circuit pur numeric astfel ca este important sa fii sigur ca aplicatia se va vinde intr-un volum mare pentru ca aceste costuri sa poata fi amortizate.

Un alt aspect este ca, in acest caz, pregatirea procesului tehnologic de fabricatie referitor la (re)dimensionarea suprafetei de siliciu pentru produse de tip ASIC dureaza mult timp, astfel ca eventualele intarzieri la lansarea produsului pe piata pot reduce profitabilitatea.

Sistemul numeric dintr-un ASIC

Sistemul numeric dintr-un ASIC care este si cel mai important sub sistem poate fi implementat prin mai multe tehnologii, functie si de scara de productie necesara.

Pentru realizarea acestuia se utilizeaza ca principale tehnologii:

- circuite total dedicate (full custom);

- circuite bazate pe celule standard (standard cell);

- circuite FPGA.

Bibliografie:

https://www.xilinx.com/

https://twitter.com/XilinxInc

https://anysilicon.com/

http://indico.ictp.it

Despre Altera nimic?

Daca studiezi arhitecturile cipurilor Altera si Xilinx, probabil vei gasi cipurile Altera mai interesante.

Xilinx tinde sa fie mai orientat spre tehnologie si sa aiba legaturi mai bune la aplicatii, oferind mai multe cipuri cu circuite personalizate care implementeaza functii specifice.

Dar, probabil va urma un articol si despre Altera ?

Nu stiu daca sunt mai interesante unele sau altele.

Dar incerc, ma lupt cu un ametit de Cyclone II, probabil cea mai ieftina si mai cheala platforma de la Intel Altera, la care am adaugat o interfata JTAG – USB-Blaster si impreuna cu Quartus 9.1 sau 13.0 vreau sa le imprietenesc fie sub WIN 7, primul, fie sub WIN 8.1 al doilea soft.

Si driverele sunt atat de… sau naiba stie ce, poate chiar dispozitivul hard USB-Blaster e vinovatul, ca nu reusesti sa nu te enervezi la fiecare incercare.

Inteleg ca nu sunt drivere disponibile pentru Win7 sau 8.1, sau exista o problema cu functionarea lor, probabil intermitenta?

Drivere ar fi pentru 7 și pentru 10. Dar win 8 și cu 8.1 sunt asa, struțocamila în ce privește abordarea driverelor.

Deși, de altfel, 8.1 este un sistem stabil și echilibrat. Nu se da răpus prea ușor. În schimb pardalnicul de USB-Blaster de la Altera cred ca asta e nărăvașul.

Îmi amintește de versurile eminesciene: îl vezi (în cpanel) și nu e! Deci da, intermitent. Joaca alba neagra. Fie îl detectează corect, fie ca device necunoscut.

Si cand te gândești ca totul e Intel.. De la platforma, CPU etc. și pana la USB blaster, Altera..

Interesant, totusi daca-s fi in locul tau as incerca ceva chestii de curiozitate. Mi-as instala un emulator de Win7 prin intermediul WMWare, sau as face update gratuit la Win10, care din punctul meu de vedere e mult mai stabil.

Am toate 3 SO instalate. Am încercat deja cu 7 și cu 8.1. Cu toate propunerile primite și siretlicurile știute de mine.

Am reușit o singura data, pe 7, sa duc pana la capăt un proiect. Un mini, un micro proiect: „Buton-not-LED”.

Deci lanțul e bun. Dar ceva în zona driver-device e putred. Am examinat fizic. Nu e. Tot soft. Scopul final e sa implementez un filtru, cel mai probabil generat cu matlab, poate chiar cu FDA Tools și exportat în VHDL sau verilog ca apoi sa îl import în Quartus.

Iar de proba, butoane și leduri. Ca nu cred ca minusculul Cyclone 2 are CAN.

Interesant, comunicati pe serial sau pe USB?

Windows PC -> USB -> Altera USB Blaster -> JTAG -> FPGA.

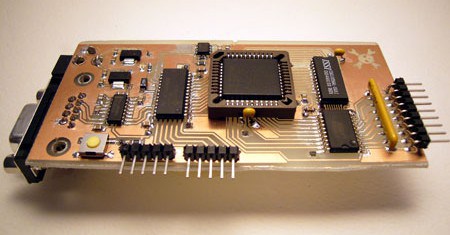

Atasat placa Altera USB Blaster.

USB-blaster-ul tau este o clona din punctul meu de vedere. Pe original ar trebui sa scrie „Altera” nu Altera-IC. De asemenea, pe placa (pcb) nu se vede nici un marcaj de componenta, cam neobisnuit pentru o placa originala. https://www.youtube.com/watch?v=FU2wybwDP1k

Da, de aceea am si pus poza cu chip-ul, ca să se vadă ca e șters (răzuit). Dar original nu se găsește.

Din ce am săpat eu pe erorile date de Windows la conectare device, cât de mult s-a putut sapa, problema tine de certificate.

Device-ul meu nu își declina identitatea și asta îl deranjează pe Windows, care ii spune stop.

Îl conectezi fizic, îl detectează, întreabă cine e și cine știe cum ii răspunde blasterul meu ca asta se supăra și îl deconectează iar în cpanel pune lămâita.

Cred ca o solutie sigura aici este fie un hack hardware pe placa, fie un modul original cumparat (o versiune mai noua daca e posibil).

Greu de înțeles dacă nu ești cel puțin la un nivel mediu cu cunoștințele de electronică digitală..

De acord. Dar cum tehnica a evoluat in domeniul electronicii, ar cam trebui ca toti cei care lucreaza in domeniu sa inteleaga.

E posibil. Recunosc că, deși am ceva cunoștințe, nu sunt, cred, la nivelul la care să mă pronunț. Probabil că sunt alți colegi de grup care o pot face..

Structurile FPGA și CPLD sunt viitorul. Procesoarele au cam ajuns la limita în ce privește tehnologiile. Nici frecventele și nici litografia nu mai ajuta. Cei doi mari jucători pe piața procesoarelor, Intel și AMD nu au plătit bani grei fără o strategie clara achiziționând primul Altera iar al doilea Xilinx.

Cei doi vectori pe care ii vad eu în evoluția procesoarelor sunt, pe de o parte, tehnologia cu grafeni/grafene, pe de alta, arhitecturile adaptive. Procesorul care se va autoreconfigura funcție de task-urile ce ii sunt alocate la un moment dat, folosind la maxim ariile de structuri, astfel încât sa nu existe timpi morți, cozi mari, gatuiri etc. Problema majora actuala sunt accelerarile și decelerarile ce apar pe canalele cu exteriorul, magistralele de legătură cu perifericele.